PCB線路板CTI數值、等級、模型及測試比較

覆銅板的耐漏電起痕性通常用相比漏電起痕指數(Comparative tracking index,簡稱CTI)表示。在覆銅箔層壓板(簡稱覆銅板)的諸多性能中,耐漏電起痕性作為一項重要的安全可靠性指標,已越來越為PCB線路板設計者和線路板生產廠家所重視。

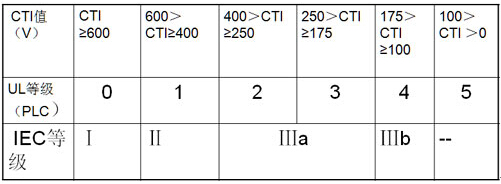

CTI值按照IEC-112標準方法《基材、印制板和印制板裝配件的相比漏電起痕指數的測試方法》測試出來,它是指基材表面經受住50滴0.1%氯化銨水溶液而沒有形成漏電痕跡的最高電壓值(V)。美國UL和IEC根據絕緣材料的CTI水平,分別將其劃分6個等級和4個等級,見表1,CTI≥600為最高等級。CTI值低的覆銅板,在高壓、高溫、潮濕、污穢等惡劣環境下長時間使用,容易產生漏電起痕。一般地,普通紙基覆銅板(XPC、FR-1等)的CTI≤150,普通復合基覆銅板(CEM-1、CEM-3)和普通玻纖布基覆銅板(FR-4)的CTI為175~225,均滿足不了電子電器產品更高安全性的使用要求。在IEC-950標準中對覆銅板的CTI和印制電路板的工作電壓、最小導線間距(最小漏電距離Minimum Creepage Distance)的關系也作了規定,CTI高的覆銅板不僅適合在高污染度、高壓場合下使用,也非常適合制作高密度印制電路板,高耐漏電起痕性覆銅板和普通覆銅板相比,用前者制作的印制電路板的線間距可允許更小。

漏電起痕Tracking:固體絕緣材料表面在電場和電解液的聯合作用下逐漸形成導電通路的過程。

相比漏電起痕指數Comparative Tracking Index (CTI):材料表面能經受住50滴電解液(0.1%氯化銨水溶液)而沒有形成漏電痕跡的最高電壓值,單位為V。

耐漏電起痕指數Proof Tracking Index(PTI):材料表面能經受住50滴電解液而沒有形成漏電痕跡的耐電壓值,以V表示。

漏電起痕模型

覆銅板CTI測試比較

提高板材CTI主要從樹脂入手,盡量減少樹脂分子結構中易碳化、易受熱分解的基因。

| 我要評論: | |

| 內 容: |

(內容最多500個漢字,1000個字符) |

| 驗證碼: | 看不清?! |

相關資訊

最新產品

同類文章排行

- 電池電路板未來趨勢:探索電池技術的無限可能

- 電路板廠獨家分享:電路板PCB相關設計指南(二)

- 5G天線PCB的工藝挑戰主要在哪些方面?

- 汽車電路板維修入門指南分享

- 5G線路板:PCB廠如何應對高精度需求

- PCB廠關于線路板制作方法的淺析

- PCB廠:什么是PCB及其特點功能解析

- PCB 特性大揭秘:常用術語深度解讀

- 關于汽車無線充電 PCB 的核心技術與設計要點剖析

- 什么是汽車電路板?它與普通電路板有什么不同?

最新資訊文章

您的瀏覽歷史

共有-條評論【我要評論】