四、PCB及線路抗干擾措施

印制線路板的抗干擾設計與具體電路有著密切的關系,這里僅就PCB抗干擾設計的幾項常用措施做一些說明。

1.電源線設計

根據印制線路板電流的大小,盡量加租電源線寬度,減少環路電阻。同時、使電源線、地線的走向和數據傳遞的方向一致,這樣有助于增強抗噪聲能力。

2.地線設計的原則

(1)數字地與模擬地分開。若線路板上既有邏輯電路又有線性電路,應使它們盡量分開。低頻電路的地應盡量采用單點并聯接地,實際布線有困難時可部分串聯后再并聯接地。高頻電路宜采用多點串聯接地,地線應短而租,高頻元件周圍盡量用柵格狀大面積地箔。

(2)接地線應盡量加粗。若接地線用很紉的線條,則接地電位隨電流的變化而變化,使抗噪性能降低。因此應將接地線加粗,使它能通過三倍于印制板上的允許電流。如有可能,接地線應在2~3mm以上。

(3)接地線構成閉環路。只由數字電路組成的印制線路板,其接地電路布成團環路大多能提高抗噪聲能力。

3.退耦電容配置

PCB設計的常規做法之一是在印制板的各個關鍵部位配置適當的退耦電容。退耦電容的一般配置原則是:

(1)電源輸入端跨接10~100uf的電解電容器。如有可能,接100uF以上的更好。

(2)原則上每個集成電路芯片都應布置一個0.01pF的瓷片電容,如遇印制板空隙不夠,可每4~8個芯片布置一個1~10pF的鉭電容。

(3)對于抗噪能力弱、關斷時電源變化大的器件,如RAM、ROM存儲器件,應在芯片的電源線和地線之間直接接入退耦電容。

(4)電容引線不能太長,尤其是高頻旁路電容不能有引線。

(5)在印制線路板中有接觸器、繼電器、按鈕等元件時.操作它們時均會產生較大火花放電,必須采用RC電路來吸收放電電流。一般R取1~2K,C取2.2~47UF。

(6) CMOS的輸入阻抗很高,且易受感應,因此在使用時對不用端要接地或接正電源。

五、PCB布線原則

在PCB設計中,布線是完成產品設計的重要步驟,可以說前面的準備工作都是為它而做的,在整個PCB中,以布線的設計過程限定最高,技巧最細、工作量最大。PCB布線有單面布線、雙面布線及多層布線。布線的方式也有兩種:自動布線及交互式布線,在自動布線之前,可以用交互式預先對要求比較嚴格的線進行布線,輸入端與輸出端的邊線應避免相鄰平行, 以免產生反射干擾。必要時應加地線隔離,兩相鄰層的布線要互相垂直,平行容易產生寄生耦合。

自動布線的布通率,依賴于良好的布局,布線規則可以預先設定,包括走線的彎曲次數、導通孔的數目、步進的數目等。一般先進行探索式布經線,快速地把短線連通,然后進行迷宮式布線,先把要布的連線進行全局的布線路徑優化,它可以根據需要斷開已布的線。 并試著重新再布線,以改進總體效果。

對目前高密度的PCB設計已感覺到貫通孔不太適應了,它浪費了許多寶貴的布線通道,為解決這一矛盾,出現了盲孔和埋孔技術,它不僅完成了導通孔的作用,還省出許多布線通道使布線過程完成得更加方便,更加流暢,更為完善,PCB板的設計過程是一個復雜而又簡單的過程,要想很好地掌握它,還需廣大電子工程設計人員去自已體會,才能得到其中的真諦。

1.電源、地線的處理

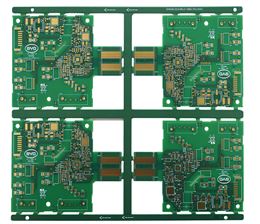

汽車BMS板

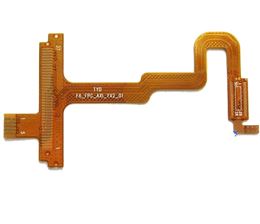

汽車BMS板 醫療設備FPC

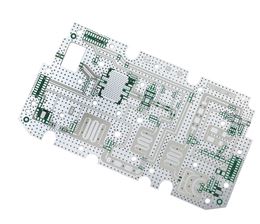

醫療設備FPC 通訊功放 PCB

通訊功放 PCB 汽車傳感器板PCB

汽車傳感器板PCB