在設計一個高性能數據采集系統時,勤奮的工程師仔細選擇一款高精度ADC,以及模擬前端調節電路所需的其他組件。在幾個星期的設計工作之后,執行仿真并優化電路原理圖,為了趕工期,設計人員迅速地將PCB板布局布線組合在一起。一個星期之后,第一個原型PCB板被測試。出乎預料,電路板性能與預期的不一樣。

這種情景在你身上發生過嗎?

最優PCB板布局布線對于使ADC達到預期的性能十分重要。當設計包含混合信號器件的電路時,你應該始終從良好的接地安排入手,并且使用最佳組件放置位置和信號路由走線將設計分為模擬、數字和電源部分。

參考路徑是ADC布局布線中最關鍵的,這是因為所有轉換都是基準電壓的一個函數。在傳統逐次逼近寄存器(SAR) ADC架構中,參考路徑也是最敏感的,其原因是基準引腳上會有一個到基準源的動態負載。

由于基準電壓在每次轉換期間被數次采樣,高電流瞬變出現在這個終端上,其中的ADC內部電容器陣列在這個位置位時被開啟和充電。基準電壓在每個轉換時鐘周期內必須保持穩定,并且穩定至所需的N位分辨率,否則的話會出現線性誤差和丟碼錯誤。

圖1顯示典型12位SAR ADC基準終端上的轉換階段期間的電流瞬變。

圖1.12位SAR ADC基準引腳上的電流瞬變

由于這些動態電流,需要使用高質量旁路電容器(CREF)對基準引腳進行去耦合操作。此旁路電容器被用作一個電荷存儲器,在這些高頻瞬變電流期間提供瞬時充電。你應該將基準旁路電容器放置在盡量靠近基準引腳的位置上,并使用較短的低電感連接將他們連接在一起。

圖2顯示了針對ADS7851,14位雙ADC(具有兩個獨立電壓基準)的PCB板布局布線示例。

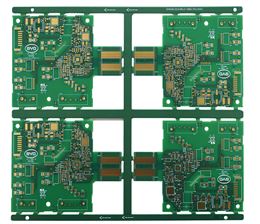

汽車BMS板

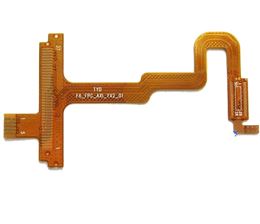

汽車BMS板 醫療設備FPC

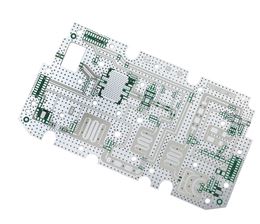

醫療設備FPC 通訊功放 PCB

通訊功放 PCB 汽車傳感器板PCB

汽車傳感器板PCB