雖然電路板廠的工程師不參與設(shè)計(jì)電路板,而是由客戶出原始設(shè)計(jì)資料再制成公司內(nèi)部的PCB電路板制作資料,但通過多年的實(shí)踐經(jīng)驗(yàn),工程師們對(duì)PCB電路板的設(shè)計(jì)早已有所積累,總結(jié)如下僅供參考:

1.如果設(shè)計(jì)的電路系統(tǒng)中包含F(xiàn)PGA器件,則在繪制原理圖前必需使用Quartus II軟件對(duì)管腳分配進(jìn)行驗(yàn)證。(FPGA中某些特殊的管腳是不能用作普通IO的)。

2.4層電路板從上到下依次為:信號(hào)平面層、地、電源、信號(hào)平面層;6層電路板從上到下依次為:信號(hào)平面層、地、信號(hào)內(nèi)電層、信號(hào)內(nèi)電層、電源、信號(hào)平面層。6層以上板(優(yōu)點(diǎn)是:防干擾輻射),優(yōu)先選擇內(nèi)電層走線,走不開選擇平面層,禁止從地或電源層走線(原因:會(huì)分割電源層,產(chǎn)生寄生效應(yīng))。

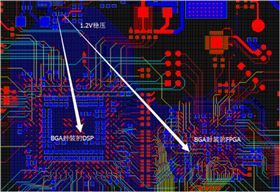

3.多電源系統(tǒng)的布線:如FPGA+DSP系統(tǒng)做6層電路板,一般至少會(huì)有3.3V+1.2V+1.8V+5V。

3.3V一般是主電源,直接鋪電源層,通過過孔很容易布通全局電源網(wǎng)絡(luò);

5V一般可能是電源輸入,只需要在一小塊區(qū)域內(nèi)鋪銅。且盡量粗(你問我該多粗——能多粗就多粗,越粗越好);

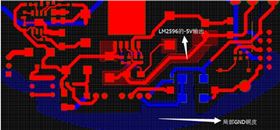

1.2V和1.8V是內(nèi)核電源(如果直接采用線連的方式會(huì)在面臨BGA器件時(shí)遇到很大困難),布局時(shí)盡量將1.2V與1.8V分開,并讓1.2V或1.8V內(nèi)相連的元件布局在緊湊的區(qū)域,使用銅皮的方式連接,如圖:

總之,因?yàn)殡娫淳W(wǎng)絡(luò)遍布整個(gè)PCB電路板,如果采用走線的方式會(huì)很復(fù)雜而且會(huì)繞很遠(yuǎn),使用鋪銅皮的方法是一種很好的選擇!

4.鄰層之間走線采用交叉方式:既可減少并行導(dǎo)線之間的電磁干擾(高中學(xué)的哦),又方便走線。

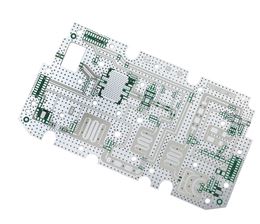

汽車BMS板

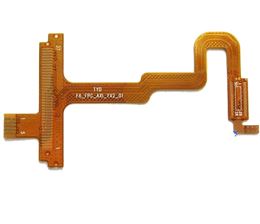

汽車BMS板 醫(yī)療設(shè)備FPC

醫(yī)療設(shè)備FPC 通訊功放 PCB

通訊功放 PCB 汽車傳感器板PCB

汽車傳感器板PCB