在進(jìn)行PCB設(shè)計(jì)時(shí),我們經(jīng)常會遇到各種各樣的問題,如阻抗匹配、EMI規(guī)則等。本文為大家整理了一些和高速PCB相關(guān)的疑難問答,希望對大家有所幫助。

1、在高速PCB設(shè)計(jì)原理圖設(shè)計(jì)時(shí),如何考慮阻抗匹配問題?

在設(shè)計(jì)高速 PCB 電路時(shí),阻抗匹配是設(shè)計(jì)的要素之一。而阻抗值跟走線方式有絕對的關(guān)系,例如是走在表面層(microstrip)或內(nèi)層(stripline/double stripline),與參考層(電源層或地層)的距離,走線寬度,PCB材質(zhì)等均會影響走線的特性阻抗值。

也就是說要在布線后才能確定阻抗值。一般仿真軟件會因線路模型或所使用的數(shù)學(xué)算法的限制而無法考慮到一些阻抗不連續(xù)的布線情況,這時(shí)候在原理圖上只能預(yù)留一些terminators(端接),如串聯(lián)電阻等,來緩和走線阻抗不連續(xù)的效應(yīng)。真正根本解決問題的方法還是布線時(shí)盡量注意避免阻抗不連續(xù)的發(fā)生。

2、當(dāng)一塊 PCB 板中有多個(gè)數(shù)/模功能塊時(shí),常規(guī)做法是要將數(shù)/模地分開,原因何在?

將數(shù)/模地分開的原因是因?yàn)閿?shù)字電路在高低電位切換時(shí)會在電源和地產(chǎn)生噪聲,噪聲的大小跟信號的速度及電流大小有關(guān)。

如果地平面上不分割且由數(shù)字區(qū)域電路所產(chǎn)生的噪聲較大而模擬區(qū)域的電路又非常接近,則即使數(shù)模信號不交叉,模擬的信號依然會被地噪聲干擾。也就是說數(shù)模地不分割的方式只能在模擬電路區(qū)域距產(chǎn)生大噪聲的數(shù)字電路區(qū)域較遠(yuǎn)時(shí)使用。

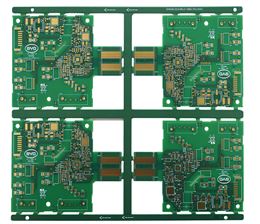

汽車BMS板

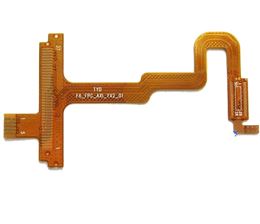

汽車BMS板 醫(yī)療設(shè)備FPC

醫(yī)療設(shè)備FPC 通訊功放 PCB

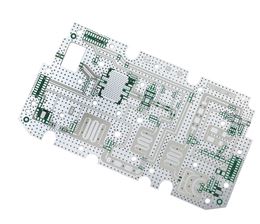

通訊功放 PCB 汽車傳感器板PCB

汽車傳感器板PCB