由于體積和尺寸都很小,對日益增長的可穿戴物聯網市場來說幾乎沒有現成的印刷電路板標準。在這些標準面世之前,我們不得不依靠在板級開發中所學的知識和制造經驗,并思考如何將它們應用于獨特的新興挑戰。有三個領域需要我們特別加以關注,它們是:電路板表面材料,射頻/微波設計和射頻傳輸線。

PCB材料

PCB電路板一般由疊層組成,這些疊層可能用纖維增強型環氧樹脂(FR4)、聚酰亞胺或羅杰斯(Rogers)材料或其它層壓材料制造。不同層之間的絕緣材料被稱為半固化片。

可穿戴設備要求很高的可靠性,因此當PCB設計師面臨著使用FR4(具有最高性價比的PCB制造材料)或更先進更昂貴材料的選擇時,這將成為一個問題。

如果可穿戴PCB應用要求高速、高頻材料,FR4可能不是最佳選擇。FR4的介電常數(Dk)是4.5,更先進的Rogers 4003系列材料的介電常數是3.55,而兄弟系列Rogers 4350的介電常數是3.66。

一個疊層的介電常數指的是疊層附近一對導體之間的電容或能量與真空中這對導體之間電容或能量的比值。在高頻時,最好是有很小的損耗,因此,介電系數為3. 66的Roger 4350比介電常數是4.5的FR4更適合更高頻率的應用。

正常情況下,可穿戴設備用的PCB層數從4層到8層。層的構建原則是,如果是8層PCB,它應能提供足夠的地層和電源層并將布線層夾在中間。這樣,串擾中的紋波效應就能保持最小,并能顯著減少電磁干擾(EMI)。

在電路板版圖設計階段,版圖安排方案一般是將大塊地層緊靠電源分配層。這樣可以形成很低的紋波效應,系統噪聲也能被減小到幾乎為零。這對射頻子系統來說尤其重要。

與Rogers材料相比,FR4具有較高的耗散因數(Df),特別是在高頻的時候。對于更高性能的FR4疊層來說,Df值在0.002左右,比普通FR4要好一個數量級。不過Rogers的疊層只有0.001或更小。當將FR4材料用于高頻應用時,就會在插損方面產生明顯的差異。插損被定義為在使用FR4、Rogers或其它材料時信號從A點傳輸到B點的功率損失。

制造問題

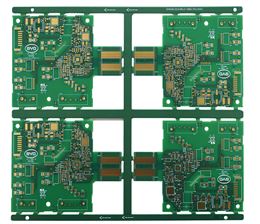

汽車BMS板

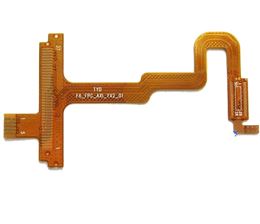

汽車BMS板 醫療設備FPC

醫療設備FPC 通訊功放 PCB

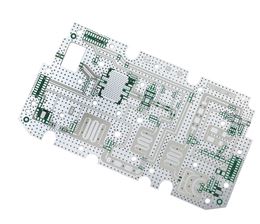

通訊功放 PCB 汽車傳感器板PCB

汽車傳感器板PCB